MIPS CPU 实现指南(零) -- 简介

Jun 29, 2019

MIPS 是一种极为优雅的 RISC 体系结构,对后世的体系结构影响深远。在后续 DEC 公司的 Alpha 以至于当前炒得火热的 RISC-V 中,我们都可以看到 MIPS 的影子。尽管 MIPS 的优雅设计不能使它在商业市场中长盛不衰,但其处理器总是能在保持简洁设计的同时获取极为高效的性能。

MIPS 一词是 “Microprocessor without Interlocked Pipelined Stage” 的缩写,也是描述处理器性能的常用单位 “Millions of Instructions Per Second” 的缩写。最初来自于 Stanford 的前辈们以 MIPS 像全世界表明了,流水线技术作为众所周知的技术并没有在体系结构中得到很好的应用,通过简洁巧妙的设计以及快速发展的 VLSI 技术,完全可以更好的利用流水线榨取更多的性能。

MIPS CPU 是 RISC CPU,RISC 这一名词来源于 UC Berkeley。这一名词为二十世纪八十年代后期出现的很多基于同一系列思想的 CPU 体系结构提供了很好的标签。有人评论说 “a RISC is any computer architecture defined after 1984”,这句话似有对 RISC 这一名词被滥用的挖苦,但道出了一个事实,即 1984 年以后的任何一款处理器设计都无法绕开 RISC 前辈们的工作。

在 MIPS 最初的二十年里有很多公司生产了基于 MIPS CPU 的设备,大家耳熟能详的 PS2 以及 N64 都是其中之一。但当前 MIPS CPU 主要是应用于嵌入式设备比如路由器或者机顶盒,甚至是这一领域也在被 ARM 等蚕食。MIPS 公司也被二度出售,一度风光的企业落得如此地步,令人惋惜。

MIPS ISA

MIPS ISA 版本较多,主要有 MIPS I~V,以及 MIPS 32/64 的六个 Release。各个版本之间的关系大致如下图所示。在我们的 CPU 中,我们实现的指令集为 MIPS 32R2 的子集。有关 MIPS 32 的详细信息,请见 官方发布的指南。

历史上的 MIPS 处理器

MIPS R2000/3000

MIPS R2000 是这一体系结构最初的实现,其五级流水线的设计与当前我们在教科书中看到的经典五段流水线类似。

后续的 R3000 主要是提升了系统频率以及添加了 FPU。但因为外部缓存的问题,这一代处理器的频率提升十分有限,直到 1991 年才勉强达到 40 MHz。

MIPS R6000

MIPS R4000

MIPS R5000

MIPS R10000

龙芯 1 号

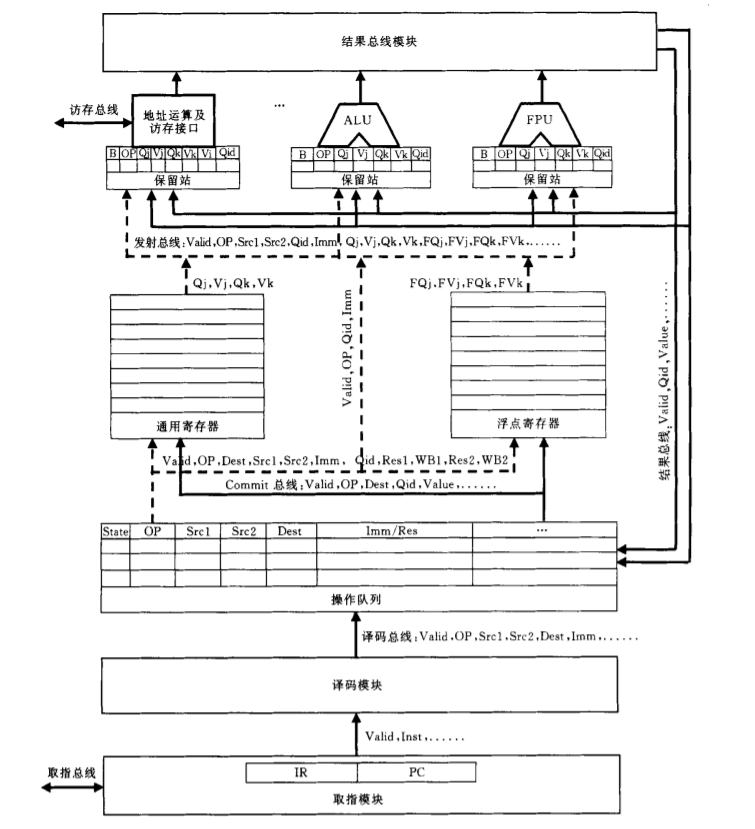

龙芯 1 号是我国第一款商品化的通用高性能芯片,采用单发射乱序执行的流水线结构,后续的龙芯 2 号系列以及龙芯 3 号系列在此基础上最高实现了四发射的乱序执行,性能跻身国际前列。

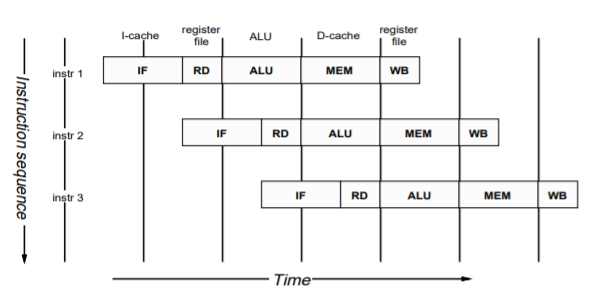

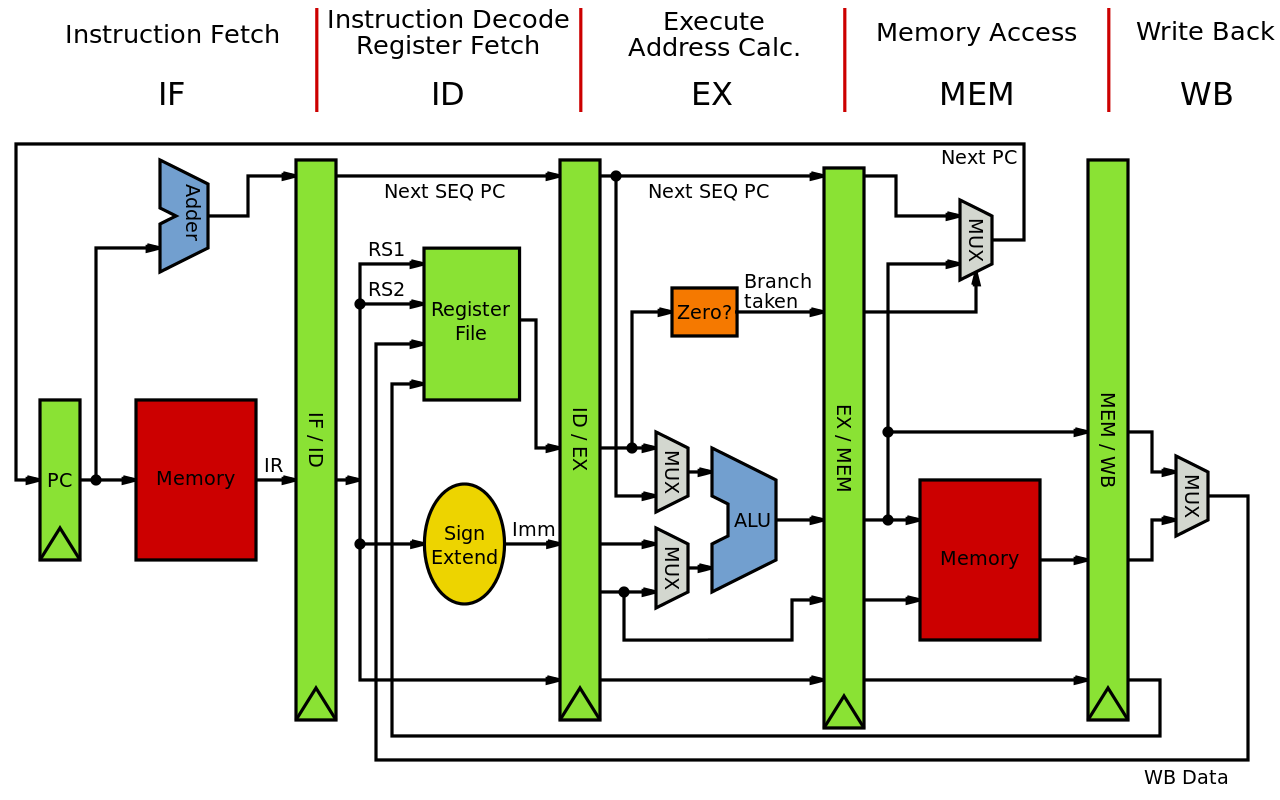

MIPS 经典五段流水线

经典的 MIPS 五段流水线与 MIPS R2000/3000 采用的设计十分相似,该流水线分为如下五个流水级:

- IF(取址) PC寄存器值作为地址,从I-Cache中取址并存储到指令寄存器。

- ID(译码) 将指令解码,并根据结果读取寄存器堆,得到指令的源操作数。

- EX(执行) 根据指令类型完成计算任务。

- MEM(访存) 访问D-Cache,不访问存储器的指令此阶段不做事。

- WB(写回) 如果指令存在目的寄存器,将指令结果写入目的寄存器。

我们在该系列文章中要实现的 CPU 的结构与此类似。

实现大纲

在这一系列指南中,我们一共会实现三个 CPU,第一个 CPU (命名为 tooYoungMIPS)是经典的五级流水线结构;第二个 CPU(命名为 tooSimpleMIPS)则在 tooYoungMIPS 的基础上添加第二条流水线,形成一个顺序超标量的设计;第三个 CPU(命名为 sometimesNaiveMIPS )则是一个比较接近现代 CPU 设计的乱序超标量处理器。

当然该指南是否会烂尾取决于我咕咕咕的水平(